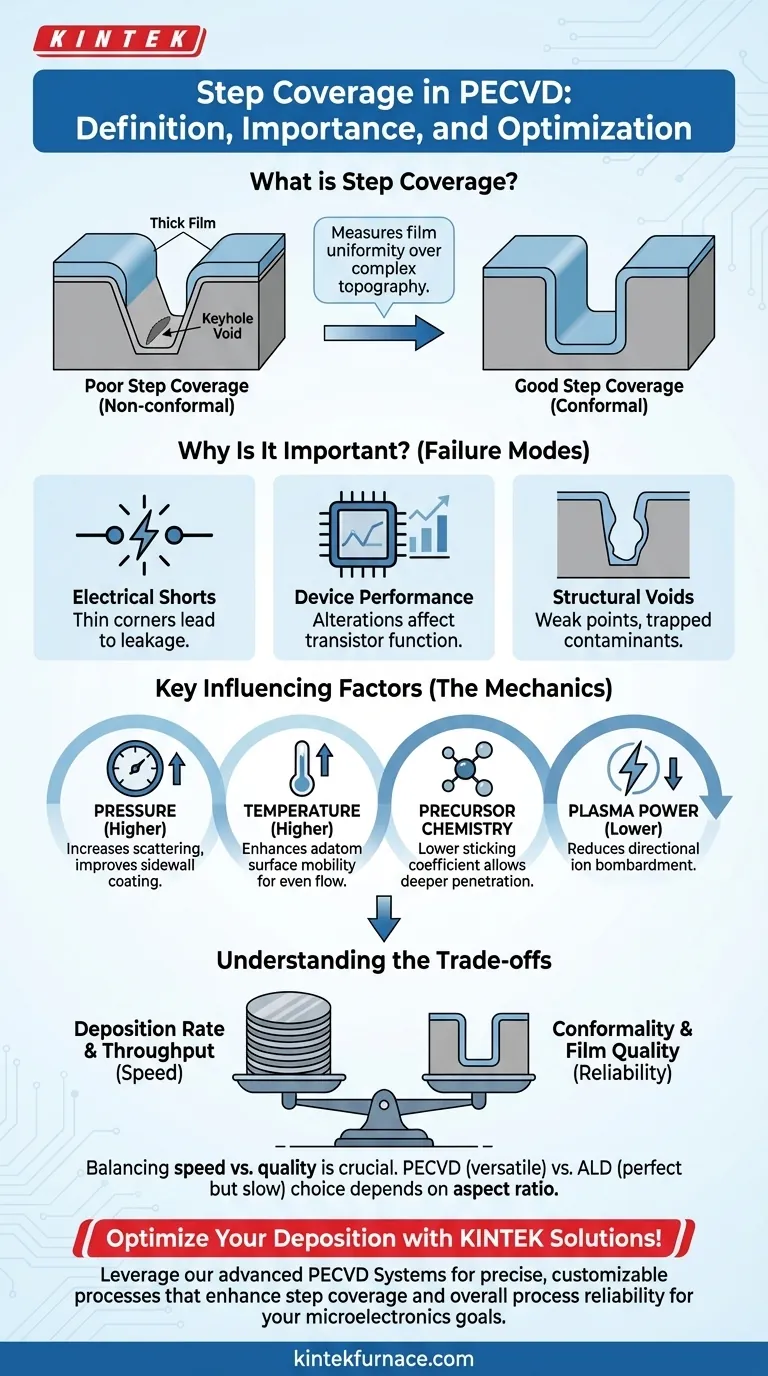

薄膜堆積において、ステップカバレッジは、堆積した膜が基板の基礎的なトポグラフィー(凹凸)にどれだけ均一に追従するかを定義する重要な尺度です。プラズマ支援化学気相成長(PECVD)の場合、これは鋭い段差、深いトレンチ、その他の複雑な三次元特徴の上で膜厚を維持する能力を測定します。この品質は単なる幾何学的な関心事ではなく、最新のマイクロエレクトロニクスデバイスの機能と信頼性にとって基本的な要件です。

ステップカバレッジの核心的な課題は、幾何学的な「遮蔽(シャドーイング)」を克服することです。これは、複雑な物体を一つの方向からスプレー塗装するのと、塗料の槽に浸すのとを比較するようなものです。PECVDはこの後者のような状態を目指し、すべての隅々まで均一なコーティングが行き渡るようにすることで、微細回路における電気的故障や構造的弱点を防ぐのに不可欠です。

PECVDにおけるステップカバレッジのメカニズム

ステップカバレッジがなぜそれほど重要なのかを理解するためには、まずそれがどのように達成されるのか、そしてどのような要因がそれに影響を与えるのかを調べる必要があります。これは、堆積種の指向性と、それらが表面に着地した後に移動する能力との間のデリケートなバランスです。

「良好」と「不良」のステップカバレッジを定義するものとは?

ステップカバレッジの品質は、通常、そのコンフォーミティ(均一性)によって記述されます。完全にコンフォーマルな膜は100%のステップカバレッジを持ち、これは特徴の上面、底面、側壁で膜厚が同一であることを意味します。

不良なステップカバレッジは非コンフォーマルです。これは、上面で膜が厚くなり、側壁で薄くなり、トレンチの底角で最も薄くなる(または存在しない)結果をもたらすことがよくあります。極端な場合、特徴の上面が底面が完全に埋まる前に閉じてしまうため、ボイド(空隙)や「キーホール」につながる可能性があります。

堆積を助けるプラズマの役割

純粋な熱プロセスとは異なり、PECVDはプラズマを使用して、より低い温度で反応性化学種を生成します。これはステップカバレッジに複雑な影響を与えます。

プラズマは反応性ラジカルの濃度を高め、遮蔽された領域での堆積を改善する可能性があります。しかし、電場も生成し、これがイオンを基板に向かって加速させ、より指向性の高い、直進的な堆積につながり、遮蔽効果を悪化させる可能性があります。鍵となるのは、これらの競合するメカニズムのバランスをとることです。

主な影響要因

良好なステップカバレッジを達成するには、いくつかのプロセスパラメータに対する正確な制御が必要です。

-

圧力: プロセス圧力が高いと、気相衝突が増加し、膜前駆体の到達がよりランダムになり、指向性が低くなります。この散乱効果により、側壁をコーティングする能力が大幅に向上します。

-

温度: 基板温度を上げると、堆積原子(アダトム)の表面移動度が向上します。これにより、それらは着地後、表面を「流れて」移動し、高濃度領域(上面の角など)から低濃度領域(トレンチの底など)へ移動し、膜厚を均一化します。

-

前駆体ガス化学: 前駆体ガスの選択は非常に重要です。寿命が長く、スティッキング係数(衝突時の付着確率)が低い分子は、反応する前に特徴内で跳ね返る可能性が高く、コンフォーミティが向上します。

-

プラズマ電力と周波数: RF電力を下げると、イオン衝撃とその関連する指向性を減らすことができ、カバレッジが向上します。プラズマの周波数(低周波か高周波か)もイオンエネルギー分布を変更し、プロセス最適化のための別の調整点を提供します。

なぜ不良なステップカバレッジがクリティカルな故障モードなのか

半導体製造において、ステップカバレッジのわずかな欠陥でさえ、デバイス全体に壊滅的な結果をもたらす可能性があります。

電気的絶縁の確保

二酸化ケイ素(SiO₂)などの誘電体膜は、導電層を絶縁するために使用されます。ステップカバレッジが不良だと、金属配線の角で膜が危険なほど薄くなります。これにより、電流リークや完全な電気的ショートにつながる弱点が生じ、回路が使用不能になります。

デバイス性能の維持

FinFETのような最新のトランジスタは複雑な3Dアーキテクチャを持っています。ゲート誘電体は、トランジスタの「フィン」の周りを完璧な均一性で包み込む必要があります。不良なステップカバレッジによるこの重要な層のわずかな薄化でさえ、トランジスタの電気的特性が変化し、予測不能な性能と早期のデバイス故障につながります。

構造的なボイドの防止

非コンフォーマルな膜が蓄積すると、トレンチの上面の角が底面よりも速く成長します。これにより、トレンチの上がピンチオフし、膜の内部にボイドまたはキーホールが密閉されることがあります。これらのボイドは、汚染物質を閉じ込めてデバイスの機械的完全性を損なう可能性のある構造的な弱点となります。

トレードオフの理解

完璧なステップカバレッジを最適化することには代償が伴います。エンジニアは、コンフォーミティと他の重要な製造指標とのバランスを取る必要があります。

堆積速度 vs. コンフォーミティ

優れたステップカバレッジを促進するプロセス条件(高圧や低電力など)は、多くの場合、堆積速度が遅くなります。大量生産において、このトレードオフはスループットとコストに直接影響します。スループットを最大化しつつ、デバイスの最小限の信頼性要件を満たすバランスを見つける必要があります。

膜質 vs. カバレッジ

表面移動度を向上させるために温度やプラズマ条件を変更することは、膜の密度、化学組成、機械的応力といった膜の固有の特性も変化させる可能性があります。カバレッジのためだけに設計された積極的なプロセスは、後で亀裂や剥離につながる、応力がかかりすぎる膜を生成する可能性があります。

PECVD vs. 代替手法

PECVDは多用途な主力技術ですが、限界もあります。最先端のロジックチップやメモリチップにおける最も要求の厳しい、高アスペクト比の特徴には、他の手法が必要になることがよくあります。例えば、原子層堆積(ALD)は、その性質上、ほぼ完璧な100%のステップカバレッジを提供しますが、PECVDよりも著しく低い堆積速度になります。

目標に合わせた適切な選択

ステップカバレッジへのアプローチは、アプリケーションの特定の要件によって決定されるべきです。

- 主な焦点が、シンプルで平面的な表面の迅速なコーティングである場合: ステップカバレッジは大きな懸念ではないため、高い堆積速度を優先できます。

- 中程度のアスペクト比(例:2:1)の特徴の絶縁が主な焦点である場合: 圧力、温度、速度のバランスを取った最適化されたPECVDプロセスが最も効果的な解決策となるでしょう。

- 高アスペクト比のトレンチ(例:10:1以上)で完璧なコンフォーミティが主な焦点である場合: スループットを犠牲にしてでも、表面移動度を高め、指向性を低減する条件を優先する必要があり、必要であればALDを代替手段として評価する必要があります。

ステップカバレッジの原則を習得することは、信頼性が高く高性能なマイクロ構造を製造するために不可欠です。

要約表:

| 側面 | 説明 |

|---|---|

| 定義 | ステップやトレンチなどの基板トポグラフィーにわたる膜厚の均一性。 |

| 重要性 | 電気的ショートを防ぎ、デバイスの信頼性を保証し、マイクロエレクトロニクスにおける構造的完全性を維持する。 |

| 主要因 | 圧力、温度、前駆体ガス化学、プラズマ電力、周波数がステップカバレッジに影響を与える。 |

| トレードオフ | 堆積速度、膜質、コンフォーミティのバランス、高アスペクト比の特徴に対するPECVD対ALD。 |

KINTEKの高度なソリューションで薄膜堆積を最適化しましょう! 優れた研究開発と社内製造を活用し、マッフル炉、チューブ炉、回転炉、真空炉・雰囲気炉、CVD/PECVDシステムなどの高温炉システムを備えた多様な研究所を提供しています。当社の強力な深いカスタマイズ能力は、お客様固有の実験ニーズとの正確な整合性を保証し、ステップカバレッジと全体的なプロセス信頼性を向上させます。マイクロエレクトロニクス製造の目標をどのようにサポートできるかについて、今すぐお問い合わせください!

ビジュアルガイド

関連製品

- 液体気化器付きスライド式PECVD管状炉(PECVD装置)

- 傾斜回転式プラズマ強化化学気相成長(PECVD)管状炉

- 化学的気相成長装置のための多加熱帯 CVD の管状炉機械

- カスタムメイド万能CVD管状炉化学蒸着CVD装置マシン

- 真空ステーションCVD装置付きスプリットチャンバーCVD管状炉