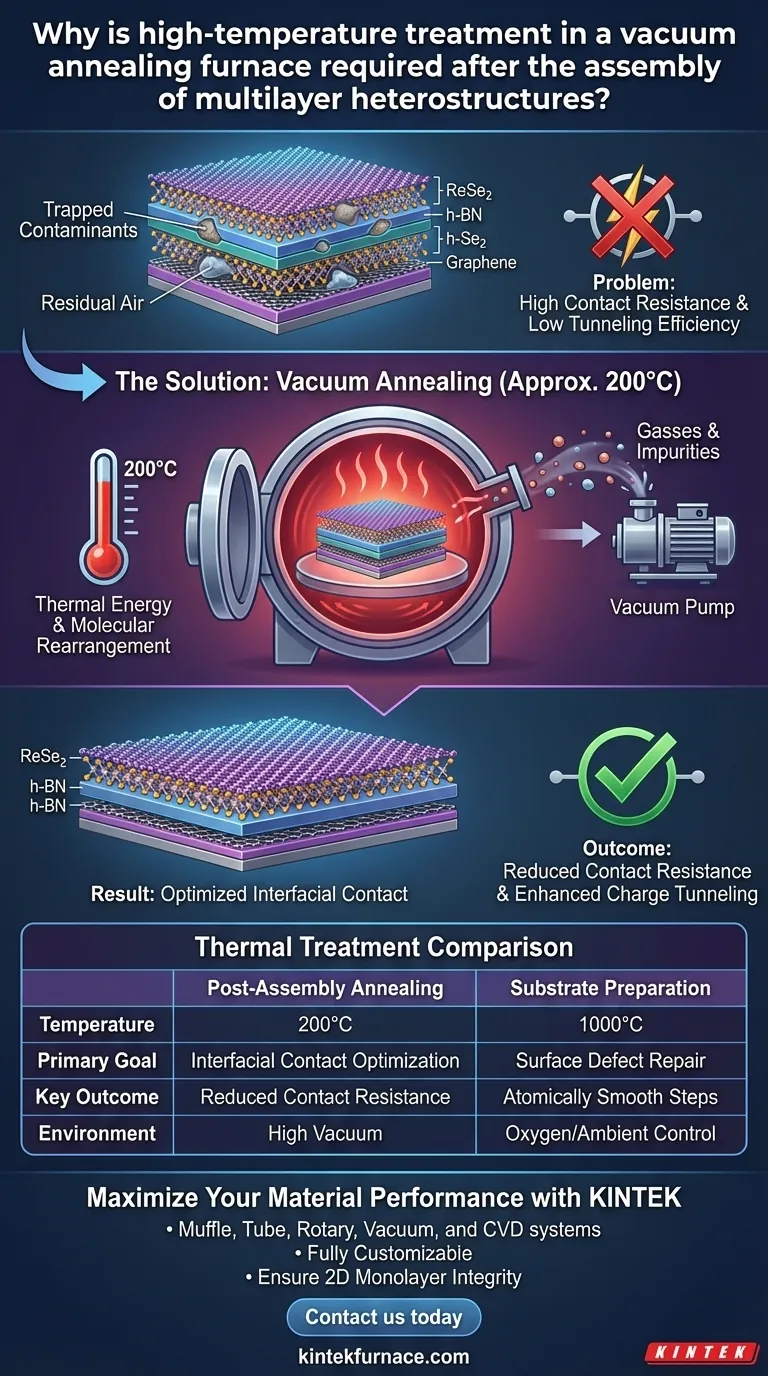

組み立て後の真空アニーリングは、重要な精製ステップです。ヘテロ構造の層間に閉じ込められた汚染物質を除去するために使用されます。通常、真空環境でデバイスを約200℃に加熱することにより、残留空気や不純物を効果的に追い出し、二次元材料をより密接な物理的接触に強制します。

この処理の主な目的は、層間の界面接触を最適化することです。閉じ込められた残留物を除去し、分子再配列を誘発することにより、プロセスは接触抵抗を大幅に低減し、高性能デバイスに不可欠な電荷トンネリング効率を向上させます。

界面改善のメカニズム

閉じ込められた汚染物質の除去

多層ヘテロ構造(ReSe2/h-BN/Grapheneなど)の物理的な積層または組み立て中に、残留空気や不純物の微視的なポケットが層間に必然的に閉じ込められます。

未処理のまま放置すると、これらの汚染物質はバリアとして機能します。これにより、原子層が量子現象を正しく機能するために必要な緊密な接触を達成できなくなります。

熱膨張と分子再配列

アニーリングプロセスは、通常、構造を約200℃で2時間加熱することを含みます。

この熱エネルギーの導入は、熱膨張を引き起こし、ヘテロ構造内の分子再配列を誘発します。材料が膨張してわずかに移動すると、閉じ込められたガスが真空中に排出され、層はより熱力学的に安定した、より平坦な構成に落ち着きます。

電気的特性の向上

よりクリーンで密接な界面の直接的な結果は、電気的性能の劇的な向上です。

具体的には、このプロセスは接触抵抗を低減し、電流が接合部をスムーズに流れることを保証します。さらに、垂直デバイスの場合、界面ギャップの除去は電荷トンネリング効率を大幅に向上させます。これは、デバイスの速度と感度の制限要因となることがよくあります。

トレードオフの理解:プロセス温度

「高温」という言葉は文脈によって意味が異なるため、組み立て後のアニーリングと基板準備を区別することが不可欠です。

過度の熱のリスク

完全に組み立てられたヘテロ構造の場合、「高温」は比較的穏やか(例:200℃)です。この範囲を大幅に超えると、繊細な2Dモノレイヤーが損傷したり、スタックコンポーネント間で望ましくない化学反応が発生したりする可能性があります。

基板処理との区別

対照的に、基板準備は、デバイスの組み立てが行われる前に、はるかに高い温度を必要とします。

基板処理プロトコルに記載されているように、ベース材料はしばしば酸素中で1000℃でアニーリングされます。この極度の熱は、有機汚染物質を除去し、表面欠陥を修復し、エピタキシャル成長のための原子レベルで滑らかなステップ構造を作成するために必要です。ただし、この温度は通常、完成した多層ヘテロ構造にとって破壊的であり、裸の基板にのみ適用する必要があります。

目標に合わせた適切な選択

最適なデバイスパフォーマンスを確保するには、製造の正しい段階で正しい熱処理を適用する必要があります。

- 完成したデバイスの最適化が主な焦点である場合:穏やかな真空アニーリング(約200℃)を利用して、閉じ込められた空気を排出し、積層された層間の電気的インターフェースを改善します。

- 材料成長の品質が主な焦点である場合:組み立て前に裸の基板に高温アニーリング(約1000℃)を利用して、原子レベルで滑らかな核生成表面を確保します。

成功は、繊細な2D層の構造的完全性を損なうことなく、界面を清掃するために熱エネルギーを使用することにかかっています。

概要表:

| 特徴 | 組み立て後のアニーリング | 基板準備 |

|---|---|---|

| 温度 | 約200℃ | 約1000℃ |

| 主な目的 | 界面接触の最適化 | 表面欠陥の修復 |

| 主な結果 | 接触抵抗の低減 | 原子レベルで滑らかなステップ |

| 環境 | 高真空 | 酸素/雰囲気制御 |

KINTEKで材料パフォーマンスを最大化しましょう

正確な熱制御は、高性能デバイスと失敗した実験の違いです。ヘテロ構造インターフェースを完成させるための穏やかな温度の真空アニーリングが必要な場合でも、基板準備のための高熱システムが必要な場合でも、KINTEKがソリューションを提供します。

専門的なR&Dと製造に裏打ちされた、マッフル、チューブ、ロータリー、真空、CVDシステムなど、幅広いシステムを提供しており、すべてお客様固有のラボ要件に合わせて完全にカスタマイズ可能です。今日、あなたの2Dモノレイヤーの完全性を確保し、優れた電荷トンネリング効率を達成してください。

研究をレベルアップする準備はできましたか? 今日お問い合わせください、あなたのアプリケーションに最適なファーネスを見つけましょう!

ビジュアルガイド

参考文献

- Wei Li, Shaoxi Wang. Reconfigurable Floating‐Gate Devices with Ambipolar ReSe<sub>2</sub> Channel: Dual‐Mode Storage, NMOS‐PMOS Transformation, Logic Functions, Synapse Simulations, Positive and Negative Photoconductive Effects. DOI: 10.1002/adfm.202425359

この記事は、以下の技術情報にも基づいています Kintek Furnace ナレッジベース .